为什么说可制造分析(DFM)比芯片还重要?

文章出处:霍尔开关原创 人气:发表时间:2020-07-21 08:37

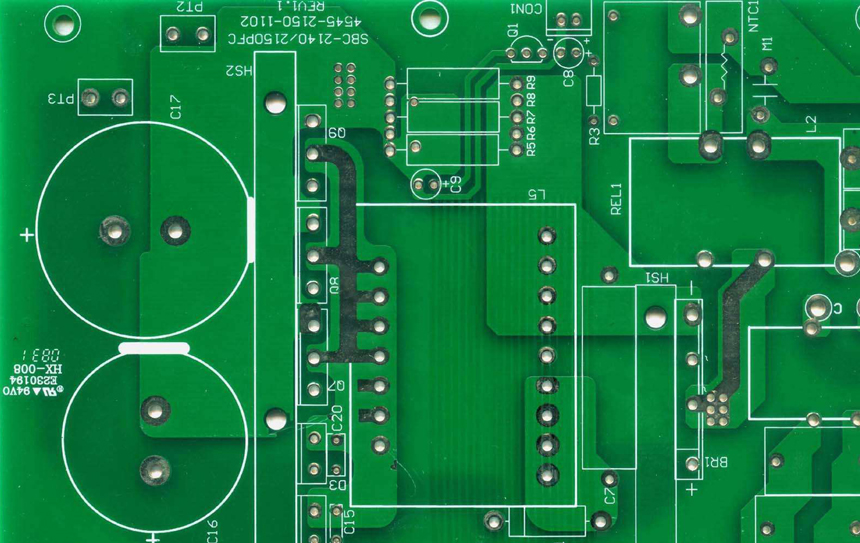

尽管围绕着可制造性设计(DFM)的价值、定义、变化性和技术争执颇多,但所有的问题都是基于芯片。当然,当我们开始考虑 28 和 7 纳米设计时,芯片 DFM 是很关键的要求。然而,关注芯片 DFM,却忽视了更重要的技术需要:面向印刷电路板的 DFM。

我们都知道即使硅片百分之百完美,如果芯片到芯片通信链接的任何一个元件(比如封装,连接头或电路板)损坏,目标系统可能仍然不能正常工作。许多封装、连接器和 PCB 供应商也许被系统设计师追逼着控制他们的加工容差。

但是,除非所有供应商一致加强规范,例如一个有正负 5%容差的连接器对 PCB 正负 10%容差的系统可能收效不大。为了优化系统设计,设计师需要研究每个元件的因果关系。迄今为止,我们没有 DFM 工具来处理诸如此类的设计问题。

在预布局设计阶段,高速系统或信号完整性工程师通常只能进行有限的 Spice 仿真。为确保系统工作正常,需要对能覆盖所有加工容差的边界情形进行仿真。

例如,PCB 内的金属线宽变化、介电堆叠高度、介电质常数和损耗正切值全部都能影响阻抗和衰减。然而,仅有较大规模公司的工程师才可能有资源来定制自有的脚本,来进行上千次仿真工作,然后再对结果进行处理。即便这样,对哪种变量进行扫描仍然没有定义完好的标准。

最明显缺乏的是封装和连接器的边界模型。对于高速设计,这些模型只能通过与频率相关的 S 参数来精确定义。然而,极少有供应商提供好的 S 参数模型,更不用说在宽范围频率内的边界模型了。

在后布局验证阶段,需要进行复杂 PCB 的精确提取和仿真,以计算详细的转角和弯曲。可是,几乎没有工具可用。

很明显,需要通用的 PCB 设计和验证方法。那么,我们需要些什么呢?

让我们关注两大领域。对预布局设计,举例来说,最好有 GUI 驱动的线路图输入编辑器,使设计师能容易地输入每个元件的变化,仿真并处理结果,报告每个变量的产生和影响。

对后布局验证,DFM 工具需要能自动调整版图以覆盖边界情形,采用快速的全波提取器来提取寄生参数,在电路仿真中用 I/O 晶体管边界模型仿真。

只有当设计师在设计和验证内都考虑了工差,他们才能说做了可制造性设计。只有当工具供应商认识到芯片只是子系统——比如 PCB——的一部分,那么 DFM 最终才能与开发终端产品的客户真正相关起来。

霍尔元件也是一种十分常见的芯片,我们在设计产品的时候,也一定要考虑到这一点。

霍尔元件也是一种十分常见的芯片,我们在设计产品的时候,也一定要考虑到这一点。

下一篇:使用霍尔传感器测量振幅的实验 上一篇:无刷直流电机和有刷直流电机的对比

同类文章排行

- 霍尔元件的BOP和BRP什么意思

- 影响霍尔元件灵敏度的因素有哪些

- 霍尔元件管脚如何定义和接线?

- 霍尔元件损坏的原因可能有哪些?

- 霍尔开关损坏的原因分析

- 迪仕科技与小米集团合作签约

- 霍尔元件NPN常开常闭和PNP常开常闭的区别

- 霍尔元件选型指南(入门篇)

- 霍尔开关应该如何接线

- 什么是线性霍尔元件

最新资讯文章

- 霍尔开关DH220/DH553在智能跳绳上的应用

- 霍尔元件代工厂华虹半导体连续刷新营收纪录

- 三星将参与收购Arm?

- 芯片厂商不敢要求降价,只求明年涨幅减半

- 消费电子芯片恐将遭受暴击型降价

- 日本被动元件,称霸全球

- 砍单潮下,芯片过剩、库存高企问题显现

- 张忠谋:解决芯片荒问题,有一个办法

- 台积电已向美国提交两份机密文件

- 日资30年电子厂关闭,称已“完成使命”

- 光刻机:美国是如何发明并彻底失去的

- 苹果A16弃3nm?业界曝关键

- Model 3零部件国产化率2年超90%,芯片呢?

- 霍尔元件的性能是如何测试的?

- 霍尔元件的应用发展分析

- 美国没有光刻机背后的原因

- 要跟Wi-Fi说再见了?

- 客户库存调整!盛群:Q4订单仍供不应求

- ST意法半导体:半导体需求热到明年

- 满坤科技积极布局PCB下游领域

苏公网安备32021302001984

苏公网安备32021302001984